# **Computer Architecture**

# Lecturer: Mihai Negru 2<sup>nd</sup> Year, Computer Science

# Lecture 4: Single-Cycle CPU Design

http://users.utcluj.ro/~negrum/

- 1. Analyze instruction set  $\rightarrow$  data-path requirements

- Write the micro-operation sequences for the target ISA

- RTL statements specify the data-path components and their interconnection

- 2. Select a set of data-path components and establish clocking methodology

- Define when storage or state elements can be read and when they can be written, e.g. clock edge-triggered

- Find the worst-time propagation delay in the data-path to determine the data-path clock cycle (CPU clock cycle)

- 3. Assemble data-path meeting the requirements

- Create an initial data-path (i.e. registers, ALU, memories)

- Establish the connectivity requirements

- Whenever <u>multiple sources</u> are connected to a <u>single input</u> (or destination), a multiplexer of appropriate size is added

- Complete the micro-operation sequences for all remaining instructions adding data path components + connections/multiplexers as needed

- 4. Identify and define the function of all control points or signals needed by the data-path

- For each instruction from the target ISA identify the values of the control signals that affect the register transfers

- 5. Assemble the control logic

- Design the control unit based on the identified control signals

- 3 main types of control unit

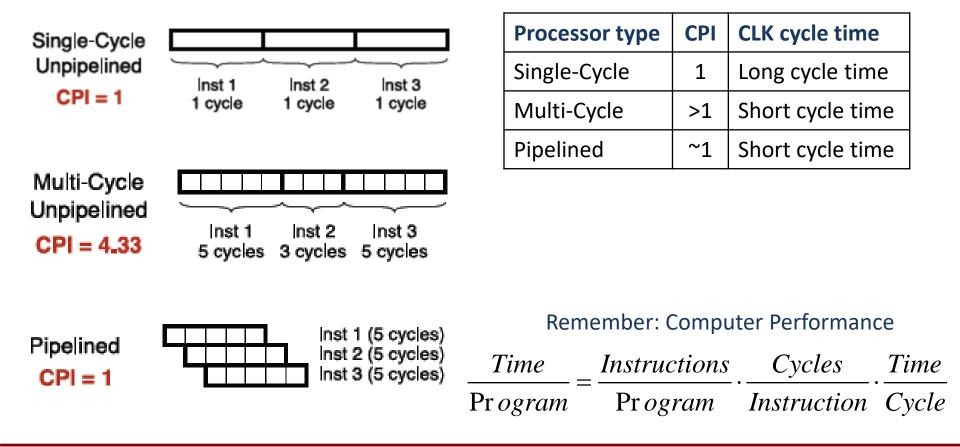

- Combinational logic  $\rightarrow$  single cycle CPU (Any instruction completed in one cycle)

- Hard-Wired: Finite-state machine implementation

- Micro-programmed

- MIPS Single-Cycle CPU Design adapted from [1]

- Design Step 1: MIPS-Lite Subset

- Select a number of representative target instructions

| Instruction          | RTL Abstract                                | Program Counter                         |

|----------------------|---------------------------------------------|-----------------------------------------|

| add \$rd, \$rs, \$rt | $RF[rd] \leftarrow RF[rs] + RF[rt]$         | PC ← PC + 4                             |

| sub \$rd, \$rs, \$rt | $RF[rd] \leftarrow RF[rs] - RF[rt]$         | $PC \leftarrow PC + 4$                  |

| ori \$rt, \$rs, imm  | $RF[rt] \leftarrow RF[rs] \mid Z\_Ext(imm)$ | $PC \leftarrow PC + 4$                  |

| lw \$rt, imm(\$rs)   | $RF[rt] \leftarrow M[RF[rs] + S_Ext(imm)]$  | $PC \leftarrow PC + 4$                  |

| sw \$rt, imm(\$rs)   | $M[RF[rs] + S\_Ext(imm)] \leftarrow RF[rt]$ | $PC \leftarrow PC + 4$                  |

| hag ért ére imm      | If(RF[rs] == RF[rt]) then                   | $PC \leftarrow PC + 4 + S_Ext(imm) <<2$ |

| beq \$rt, \$rs, imm  | else                                        | $PC \leftarrow PC + 4$                  |

- RTL Abstract defines the behavior of each instruction

- Remember the instruction execution cycle (previous lecture)

- IF, ID/OF, EX, MEM, WB

- IF, ID and OF are common for all instructions

$PC \leftarrow PC + 4$

#### • R-type Instructions

- Basic operation:

- Next instruction PC:

- OPCODE is always Zero for R-type Instructions

| 31 26   | 25 21 | 20 16 | 15 11 | 10 6  | 5 0    | ) |

|---------|-------|-------|-------|-------|--------|---|

| SPECIAL |       |       |       | 0     | ADD    |   |

| 000000  | rs    | rt    | rd    | 00000 | 100000 |   |

| 6       | 5     | 5     | 5     | 5     | 6      | - |

$RF[rd] \leftarrow RF[rs] \text{ op } RF[rt]$

- ADD \$rd, \$rs, \$rt

- $RF[rd] \leftarrow RF[rs] + RF[rt]$

- PC ← PC + 4

- Add signed 32-bit numbers.

- Exception on OVERFLOW

- Addressing Modes

- Register direct

|       | Necessary Resources              |  |  |  |  |  |

|-------|----------------------------------|--|--|--|--|--|

| IF    | PC, Instr. Memory, Adder         |  |  |  |  |  |

| ID/OF | Register File, Main Control Unit |  |  |  |  |  |

| EX    | ALU, ALU Control Unit            |  |  |  |  |  |

| MEM   | No operation                     |  |  |  |  |  |

| WB    | Register File                    |  |  |  |  |  |

- I-type Instructions: Load Word LW

- Load a word (32 bits) from the Data Memory into a Register

| _31 | L 26         | 25 23 | L <u>20 16</u> | 15 0                |

|-----|--------------|-------|----------------|---------------------|

|     | LW<br>100011 | rs    | rt             | address / immediate |

|     | 6            | 5     | 5              | 16                  |

## • lw \$rt, imm(\$rs)

- $RF[rt] \leftarrow M[RF[rs] + S_Ext(imm)]$

- $PC \leftarrow PC + 4$

- Addressing Modes

- Register Direct

- Base addressing

|       | Necessary Resources                        |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

| IF    | PC, Instr. Memory, Adder                   |  |  |  |  |  |

| ID/OF | Register File, Main Control Unit, Extender |  |  |  |  |  |

| EX    | ALU, ALU Control Unit                      |  |  |  |  |  |

| MEM   | Data Memory MUX                            |  |  |  |  |  |

| WB    | Register File                              |  |  |  |  |  |

- I-type Instructions: Store Word SW

- Store a word (32-bits) from the Register File in the Data Memory

| 3 | 1 26         | 25 21 | 20 16 | 15 0                |

|---|--------------|-------|-------|---------------------|

|   | SW<br>101011 | rs    | rt    | address / immediate |

|   | 6            | 5     | 5     | 16                  |

### • sw \$rt, imm(\$rs)

- $M[RF[rs] + S\_Ext(imm)] \leftarrow RF[rt]$

- $PC \leftarrow PC + 4$

- Addressing Modes

- Register Direct

- Base addressing

|       | Necessary Resources                        |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

| IF    | PC, Instr. Memory, Adder                   |  |  |  |  |  |

| ID/OF | Register File, Main Control Unit, Extender |  |  |  |  |  |

| EX    | ALU, ALU Control Unit                      |  |  |  |  |  |

| MEM   | Data Memory                                |  |  |  |  |  |

| WB    | No operation                               |  |  |  |  |  |

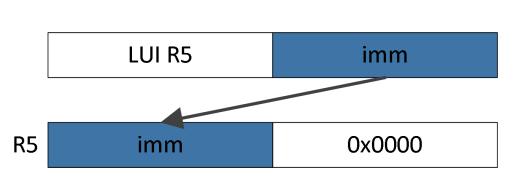

- I-type Instructions: Load Upper Immediate LUI

- Load a constant in high part of a word

| 31 26         | 25 21 | 20 16 | 15 0                |

|---------------|-------|-------|---------------------|

| LUI<br>001111 | rs    | rt    | address / immediate |

| 6             | 5     | 5     | 16                  |

- lui \$rt, imm

- RF[rt] ← imm || 0x0000

- $PC \leftarrow PC + 4$

- Addressing Modes

- Register direct

- Used to form 32 bits constants with ORI

- Additional Resources: shifter implemented in the ALU

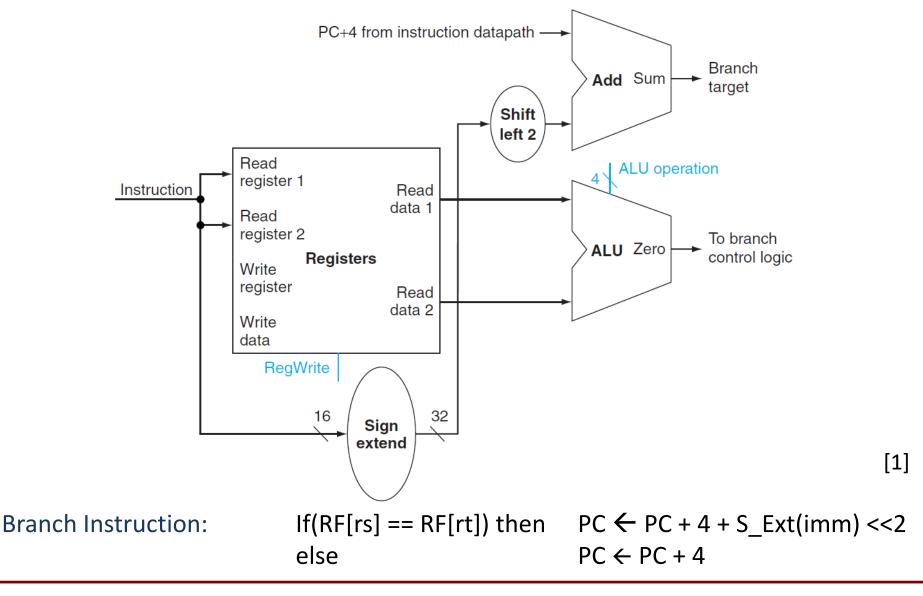

- I-type Instructions: Branch on Equal BEQ

- Compare two registers, then perform a conditional jump relative to the PC

| 31        | 26 25     | 21 | 20 16 | 15 0                |

|-----------|-----------|----|-------|---------------------|

| BE<br>000 | EQ<br>100 | rs | rt    | address / immediate |

| 6         | 5         | 5  | 5     | 16                  |

### • beq \$rt, \$rs, imm

- If(RF[rs] == RF[rt])  $\rightarrow$  PC  $\leftarrow$  PC + 4 + S\_Ext(imm) << 2 else PC  $\leftarrow$  PC + 4

- Addressing Modes

- PC-relative addressing

- If condition is not true

- Sequential execution, + 4

- If condition is true

- Jump, PC + 4 + S\_Ext(imm)<<2

|   | Necessary Resources |                                            |  |  |  |  |  |

|---|---------------------|--------------------------------------------|--|--|--|--|--|

|   | IF                  | PC, Instr. Memory, Adder, Adder, MUX       |  |  |  |  |  |

|   | ID/OF               | Register File, Main Control Unit, Extender |  |  |  |  |  |

|   | EX                  | ALU, ALU Control Unit                      |  |  |  |  |  |

| 2 | MEM                 | No operation                               |  |  |  |  |  |

| ۷ | WB                  | No operation                               |  |  |  |  |  |

- Needed Resources (so far)

- PC Program Counter

- Memories

- Instruction and Data Memory

- Register File (32 x 32 bits)

- Read R[rs], Read R[rt]

- Write R[rd] or R[rt]

- Shift Left 2

- ALU Arithmetic Logic Unit MUX

**MUX**

- Arithmetic or Logical operations with two registers

- Arithmetic or Logical operations with one register and an extended immediate value

- Add PC with 4 or with 4 + Sign Extended Immediate << 2 for next instructions address (PC) computation MUX

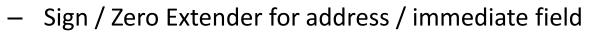

#### • Design Step 2: Data-Path Components

- Program Counter PC

- 32-bit positive edge triggered D flip-flop

- Instruction Memory (ideal ROM model)

- One input bus: Instruction address

- One output bus: Instruction

- Memory word is selected by Instruction address, no control signals

- Adder

- 32-bit Ripple Carry Adder to form the next instruction address

## Single-Cycle CPU Design – Step 2

[1]

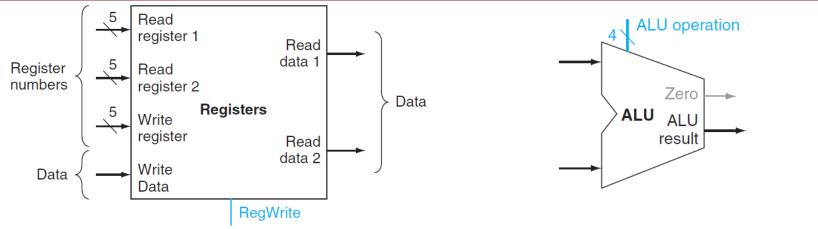

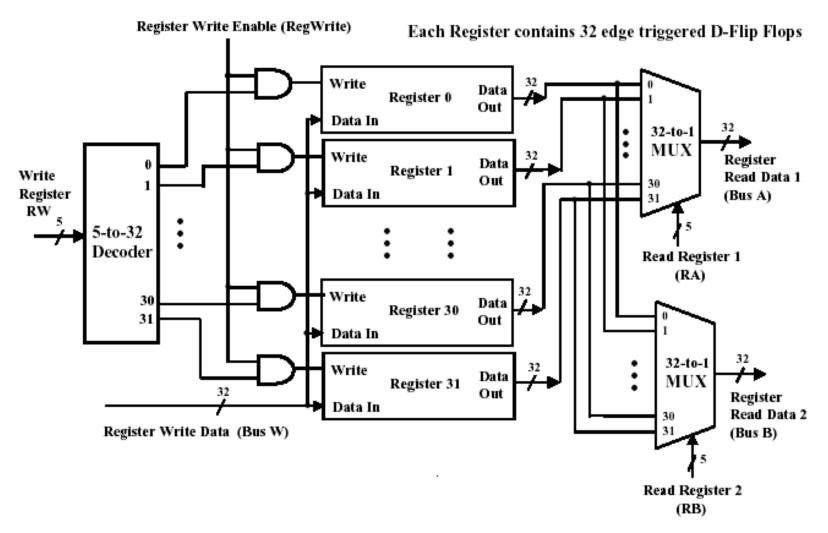

- Register File 32x32-bits

- Built using D flip-flops (didactic model), SRAM in real machines

- Two 32-bit data outputs: Read data 1 and Read data 2

- One 32-bit data input: Write data

- Multi-access: 2 asynchronous Reads + 1 edge triggered Write in the same clock period

- Read register 1 selects the register to put on Read data 1 output

- Read register 2 selects the register to put on Read data 2 output

- Write register selects the register to be written by Write Data when RegWrite is asserted

- During read operation, Registers behaves as a combinational logic block

- Arithmetic Logic Unit ALU

- Designed according to ISA requirements

#### **Register File Implementation**

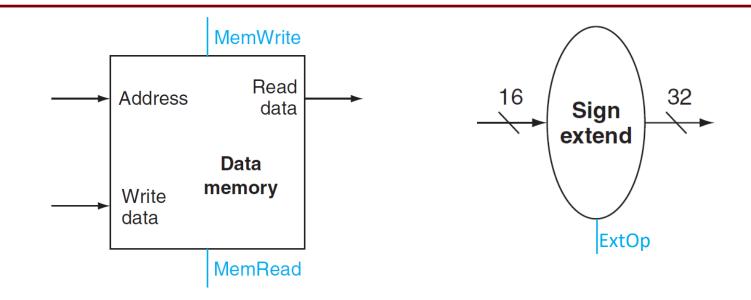

- Data Memory (ideal SRAM model)

- Two input buses: Address and Write data

- One output bus: Read data

- Two control signals: MemRead and MemWrite

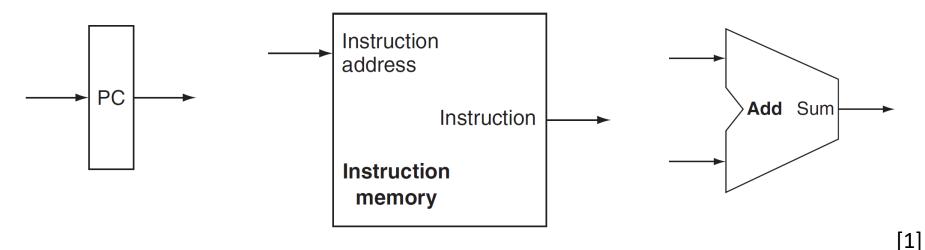

- Sign Extension Unit

- The control signal will only be added later

- ExtOp = 1  $\rightarrow$  Sign Extender

- ExtOp =  $0 \rightarrow$  Zero Extender

- Design Step 2: Clocking Methodology

- Clocking methodology defines when signals can be read and written

- Determines when data is valid and stable relative to the clock

- Clocking alternatives

- Falling edge triggered system

- Rising edge triggered system

- Two phase clocking

- All storage elements (e.g. Flip-Flops, Registers, Data Memory) writes are triggered by the same clock edge.

- Usually, State elements are written on every clock cycle

- If not, we need an explicit write control signal.

- Write only when both the write control is asserted and the clock edge occurs

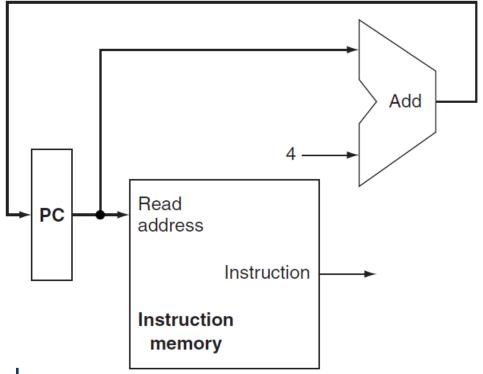

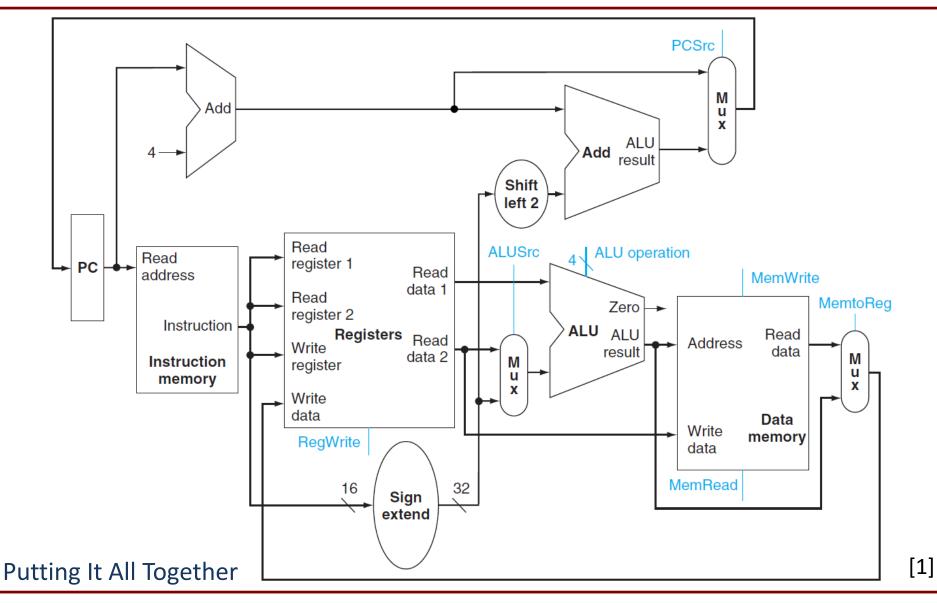

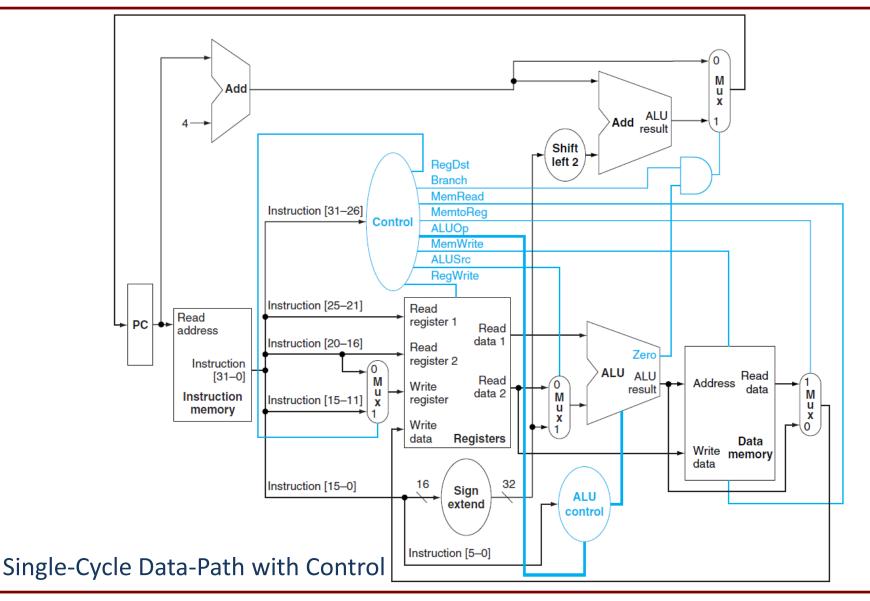

• Design Step 3: Assemble Data-Path – Single-Cycle

#### **Instruction Fetch**

- 32-bit Program Counter, 32-bit Adder and instruction Memory

- − Instruction  $\leftarrow$  IM[PC]; PC  $\leftarrow$  PC + 4

# Single-Cycle CPU Design – Step 3

R-type Instructions: I-type Instruction – Load: I-type Instruction – Store:  $RF[rd] \leftarrow RF[rs] \text{ op } RF[rt]$   $RF[rt] \leftarrow M[RF[rs] + S\_Ext(imm)]$  $M[RF[rs] + S\_Ext(imm)] \leftarrow RF[rt]$

••••

2024

Cluj-Napoca

#### Cluj-Napoca

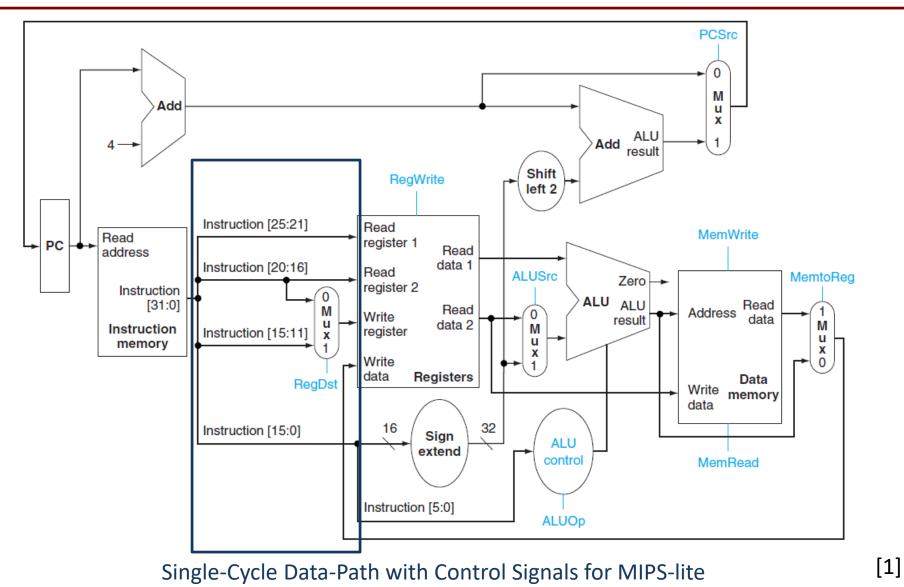

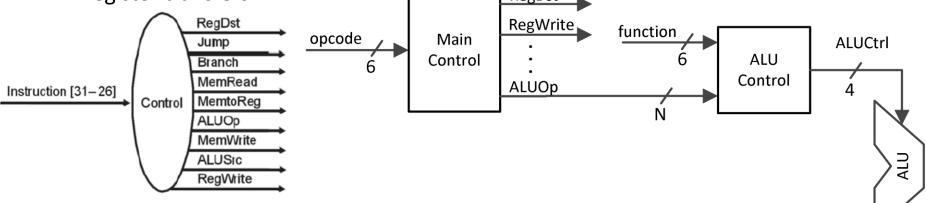

- Design Step 4: Identifying the Control Signals

- Identify and define the function of all control signals needed by the data-path

- Analyze each instruction to determine the setting of control points that affect the register transfers

#### The main control signal values for MIPS-lite

| Instruction | Reg | Reg   | ALU | РС  | Mem  | Mem   | Memto | ALU |

|-------------|-----|-------|-----|-----|------|-------|-------|-----|

| Instruction | Dst | Write | Src | Src | Read | Write | Reg   | Ор  |

| R- format   | 1   | 1     | 0   | 0   | 0    | 0     | 0     | 10  |

| lw          | 0   | 1     | 1   | 0   | 1    | 0     | 1     | 00  |

| SW          | Х   | 0     | 1   | 0   | 0    | 1     | Х     | 00  |

| beq         | Х   | 0     | 0   | 1   | 0    | 0     | Х     | 01  |

| Signal name | Effect when deasserted (0)               | Effect when asserted (1)                    |  |  |  |  |

|-------------|------------------------------------------|---------------------------------------------|--|--|--|--|

| PogDet      | The register destination number for the  | The register destination number for the     |  |  |  |  |

| RegDst      | Write register comes from the rt field   | Write register comes from the rd field      |  |  |  |  |

|             |                                          | The register on the Write register input is |  |  |  |  |

| RegWrite    | None                                     | written into with the value on the Write    |  |  |  |  |

|             |                                          | data input                                  |  |  |  |  |

| ALUSrc      | The second ALU operand comes from the    | The second ALU operand is the sign-         |  |  |  |  |

| ALUSIC      | second Register file output              | extended lower 16-bits of the instruction   |  |  |  |  |

| PCSrc       | The PC is replaced by the output of the  | The PC is replaced by the output of the     |  |  |  |  |

|             | adder that computes the value of PC + 4  | adder that computes the branch address      |  |  |  |  |

| MemRead     | None                                     | Data memory contents at the read            |  |  |  |  |

| Memkeau     | None                                     | address are put on read data output         |  |  |  |  |

|             |                                          | Data memory contents at address given by    |  |  |  |  |

| MemWrite    | None                                     | write address is replaced by value on write |  |  |  |  |

|             |                                          | data input                                  |  |  |  |  |

| MemtoReg    | The value fed to the register write data | The value fed to the register write data    |  |  |  |  |

| weintoneg   | input comes from the ALU                 | input comes from the data memory            |  |  |  |  |

|             |                                          |                                             |  |  |  |  |

The Meaning of the Control Signals

ALUOp – defines the behavior of the ALU control PCSrc = Branch AND Zero

## Single-Cycle CPU Design – Step 4

2024

[1]

| Instruction<br>Opcode | ALUOp | Instruction<br>Operation | Function<br>Field | Desired<br>ALU Operation | ALU<br>Control |

|-----------------------|-------|--------------------------|-------------------|--------------------------|----------------|

| LW                    | 00    | load word                | XXXXXX            | add                      | 0010           |

| SW                    | 00    | store word               | XXXXXX            | add                      | 0010           |

| Branch equal          | 01    | branch equal             | XXXXXX            | subtract                 | 0110           |

| R-type                | 10    | add                      | 100000            | add                      | 0010           |

| R-type                | 10    | subtract                 | 100010            | subtract                 | 0110           |

| R-type                | 10    | and                      | 100100            | and                      | 0000           |

| R-type                | 10    | or                       | 100101            | or                       | 0001           |

| R-type                | 10    | set on less than         | 101010            | set on less than         | 0111           |

Local Control for the ALU

$\mathsf{opcode} \xrightarrow{\rightarrow} \mathsf{ALUOp} \xrightarrow{\rightarrow} \mathsf{ALUCtrl}$

Our example uses 2-bits for ALUOp. It can be further extended if necessary

## Single-Cycle CPU Design – Step 4

[1]

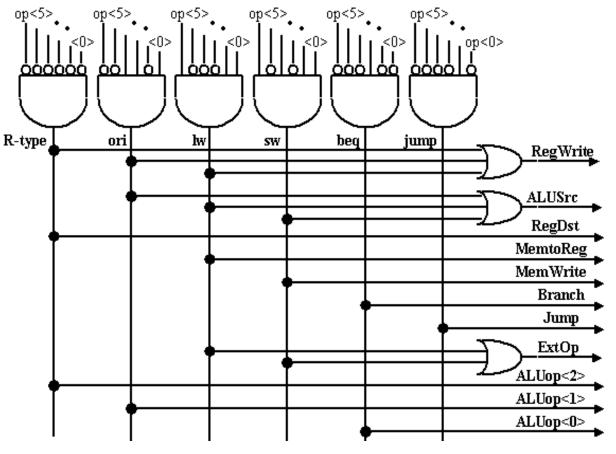

- Design Step 5: Implement the Control

- Only combinational logic is needed for the Single-Cycle Control

A possible PLA implementation of the Main Control Unit

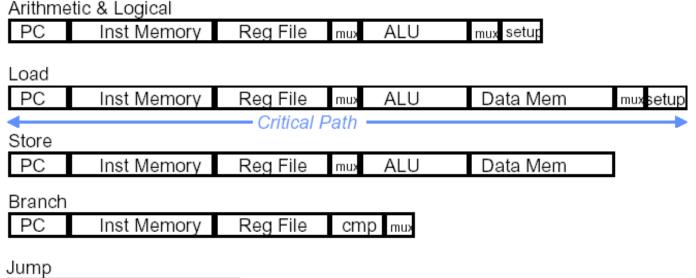

- Critical Path

- Load Word operation: PC's Clk-to-Q + Instruction Memory's Access Time + Register File's Access Time + ALU to Perform a 32-bit Add + Data Memory Access Time + Setup Time for Register File Write + Clock Skew

| oump |             |     |

|------|-------------|-----|

| PC   | Inst Memory | mux |

#### Single cycle: Instruction Timing Comparison

- Single-Cycle disadvantages

- The clock cycle is chosen to fullfill the critical path (lw)  $\rightarrow$  slow clock

- The time needed for a load is much larger than for other instructions

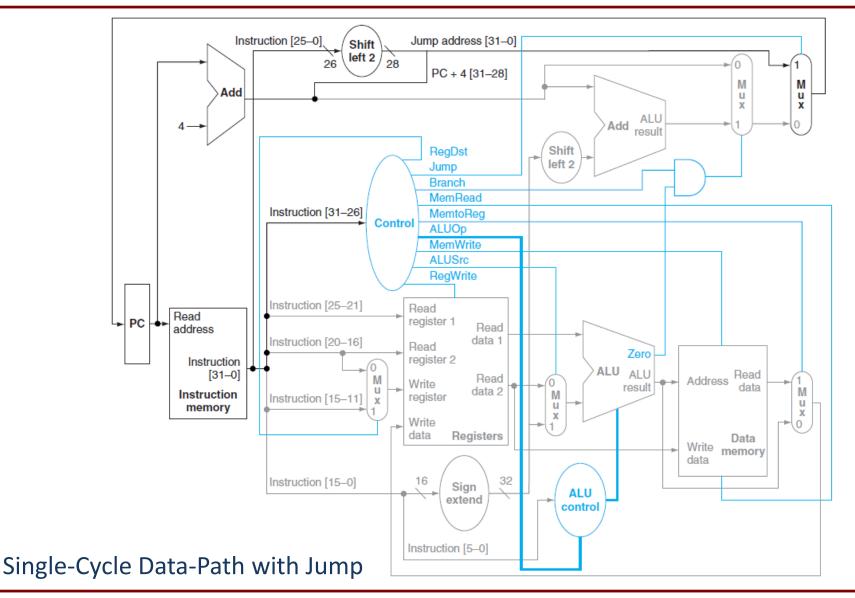

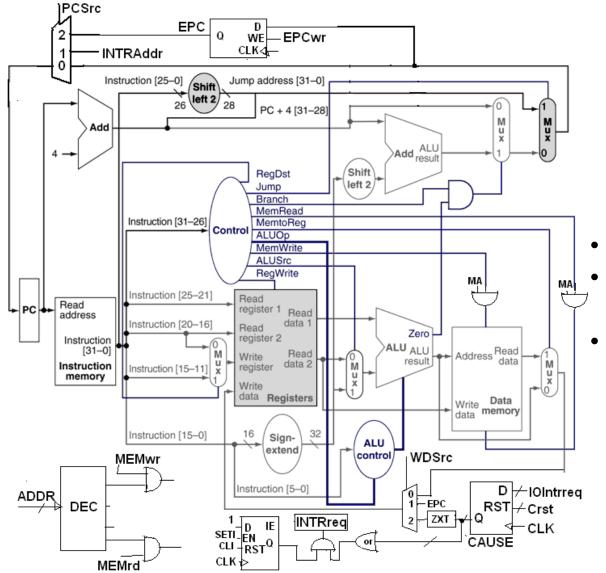

#### • Single-Cycle CPU Extensions

- Problem: define some ports for I/O communication

- A convenient solution (without introducing dedicated instructions)

- I/O mapped through the memory address space

- Some addresses from data memory will be reserved for I/O ports

- Writing and reading to this I/O ports is carried out by using the standard instructions for memory accesses (Iw and sw)

- LW and SW used for word (32-bits) transfers (use LH and SH for half words, LB and SB for bytes)

- You need to specify in the RTL description how to handle the reserved addresses for peripherals. From RTL will result the necessary supplementary components (address decoders, etc.)

#### Connecting I/O Devices

- Devices are mapped through the memory address space

- 2 INPUTS

- 1 OUTPUT

- Control Signals:

- MemRead

- MemWrite

- MA

#### MIPS Interrupt Mechanism

- IE Interrupt Enable ZXT – Zero Extender

- See the previous course

- Implement other instructions for the Single-Cycle MIPS CPU

- add, sub, and, or, lw, sw, beq, j, addi, andi, ori

- sll, srl, sra, sllv, srlv, srav

- slt, slti

- bne , bgez, bltz,...

- jr, jal

- ....

- Implement new instructions for the Single-Cycle MIPS CPU

- LWR, SWR (sums two registers to obtain the memory address)

- LWA, SWA (uses a single register to obtain the memory address)

- SWAP two registers

- Arithmetic/logical instructions with memory operands

- addm \$t2, 100(\$t3) \$t2 ← \$t2 + M[\$t3+100]

- D. A. Patterson, J. L. Hennessy, "Computer Organization and Design: The Hardware/Software Interface", 5<sup>th</sup> edition, ed. Morgan–Kaufmann, 2013.

- D. A. Patterson and J. L. Hennessy, "Computer Organization and Design: A Quantitative Approach", 5<sup>th</sup> edition, ed. Morgan-Kaufmann, 2011.

- 3. MIPS32<sup>™</sup> Architecture for Programmers, Volume I: "Introduction to the MIPS32<sup>™</sup> Architecture".

- MIPS32<sup>™</sup> Architecture for Programmers Volume II: "The MIPS32<sup>™</sup> Instruction Set".